आज की स्टोरेज प्रणालियाँ न केवल टेराबिट्स पर बढ़ती हैं और डेटा स्थानांतरण दर अधिक होती है, बल्कि कम ऊर्जा की आवश्यकता भी होती है और कम जगह घेरती हैं। इन प्रणालियों को अधिक लचीलापन प्रदान करने के लिए बेहतर कनेक्टिविटी की भी आवश्यकता होती है। डिज़ाइनरों को आज या भविष्य में आवश्यक डेटा दर प्रदान करने के लिए छोटे इंटरकनेक्ट की आवश्यकता होती है। और जन्म से विकास और धीरे-धीरे परिपक्व होने तक का एक मानक एक दिन का काम नहीं है। विशेष रूप से आईटी उद्योग में, कोई भी तकनीक लगातार बेहतर होती रहती है और खुद को विकसित करती रहती है, जैसा कि सीरियल अटैच्ड एससीएसआई (एसएएस) विनिर्देश है। समानांतर एससीएसआई के उत्तराधिकारी के रूप में, एसएएस विनिर्देश कुछ समय से मौजूद है।

SAS के विकास के वर्षों में, इसके विनिर्देशों में सुधार हुआ है। हालाँकि अंतर्निहित प्रोटोकॉल को बरकरार रखा गया है, मूल रूप से बहुत अधिक परिवर्तन नहीं हुए हैं, लेकिन बाहरी इंटरफ़ेस कनेक्टर के विनिर्देशों में कई बदलाव हुए हैं, जो SAS द्वारा बाज़ार के माहौल के अनुकूल होने के लिए किया गया एक समायोजन है। इन "हज़ार मील की ओर बढ़ते कदम" निरंतर सुधार के साथ, SAS विनिर्देश अधिक परिपक्व होते गए हैं। विभिन्न विनिर्देशों वाले इंटरफ़ेस कनेक्टरों को SAS कहा जाता है, और समानांतर से धारावाहिक, समानांतर SCSI तकनीक से धारावाहिक कनेक्टेड SCSI (SAS) तकनीक में परिवर्तन ने केबल रूटिंग योजना को बहुत बदल दिया है। पिछला समानांतर SCSI 320Mb/s तक की गति से 16 चैनलों पर सिंगल-एंडेड या डिफरेंशियल संचालित कर सकता था। वर्तमान में, एंटरप्राइज़ स्टोरेज क्षेत्र में अधिक सामान्य SAS3.0 इंटरफ़ेस अभी भी बाज़ार में उपयोग किया जाता है, लेकिन इसकी बैंडविड्थ SAS3 की तुलना में दोगुनी तेज़ है, जिसे लंबे समय से अपग्रेड नहीं किया गया है, जो 24Gbps है, जो सामान्य PCIe3.0×4 सॉलिड-स्टेट ड्राइव की बैंडविड्थ का लगभग 75% है। SAS-4 विनिर्देश में वर्णित नवीनतम MiniSAS कनेक्टर छोटा है और उच्च घनत्व प्रदान करता है। नवीनतम Mini-SAS कनेक्टर मूल SCSI कनेक्टर के आकार का आधा और SAS कनेक्टर के आकार का 70% है। मूल SCSI समानांतर केबल के विपरीत, SAS और Mini SAS दोनों में चार चैनल होते हैं। हालाँकि, उच्च गति, उच्च घनत्व और अधिक लचीलेपन के अलावा, जटिलता में भी वृद्धि होती है। कनेक्टर के छोटे आकार के कारण, मूल केबल निर्माता, केबल असेंबलर और सिस्टम डिज़ाइनर को केबल असेंबली के दौरान सिग्नल अखंडता मापदंडों पर पूरा ध्यान देना चाहिए।

सभी केबल असेंबलर स्टोरेज सिस्टम की सिग्नल अखंडता आवश्यकताओं को पूरा करने के लिए उच्च-गुणवत्ता वाले हाई-स्पीड सिग्नल प्रदान करने में सक्षम नहीं होते हैं। केबल असेंबलरों को नवीनतम स्टोरेज सिस्टम के लिए उच्च-गुणवत्ता और लागत-प्रभावी समाधानों की आवश्यकता होती है। स्थिर, टिकाऊ हाई-स्पीड केबल असेंबलियों का उत्पादन करने के लिए, कई कारकों पर विचार करने की आवश्यकता होती है। मशीनिंग और प्रसंस्करण की गुणवत्ता बनाए रखने के अलावा, डिजाइनरों को सिग्नल अखंडता मापदंडों पर भी ध्यान देना चाहिए जो आज के हाई-स्पीड मेमोरी डिवाइस केबल्स को संभव बनाते हैं।

सिग्नल अखंडता विनिर्देश (कौन सा सिग्नल पूर्ण है?)

सिग्नल अखंडता के कुछ मुख्य मापदंडों में सम्मिलन हानि, निकट-अंत और दूर-अंत क्रॉसटॉक, वापसी हानि, अंतर युग्म का आंतरिक रूप से तिरछा विरूपण, और अंतर मोड से सामान्य मोड तक का आयाम शामिल हैं। हालाँकि ये कारक आपस में जुड़े हुए हैं और एक-दूसरे को प्रभावित करते हैं, फिर भी हम इसके मुख्य प्रभाव का अध्ययन करने के लिए एक समय में एक कारक पर विचार कर सकते हैं।

सम्मिलन हानि (उच्च आवृत्ति पैरामीटर मूल बातें 01- क्षीणन पैरामीटर)

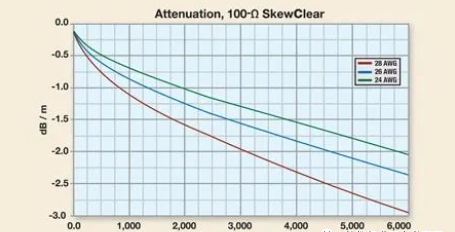

केबल के संचारण सिरे से प्राप्तकर्ता सिरे तक सिग्नल के आयाम में होने वाली हानि को इंसर्शन लॉस कहते हैं, जो आवृत्ति के समानुपाती होता है। इंसर्शन लॉस तार संख्या पर भी निर्भर करता है, जैसा कि नीचे दिए गए क्षीणन आरेख में दिखाया गया है। 30 या 28-AWG केबल के कम दूरी के आंतरिक घटकों के लिए, एक अच्छी गुणवत्ता वाली केबल में 1.5GHz पर 2dB/m से कम क्षीणन होना चाहिए। 10 मीटर केबल का उपयोग करने वाले बाहरी 6Gb/s SAS के लिए, 24 के औसत लाइन गेज वाले केबल की अनुशंसा की जाती है, जिसमें 3GHz पर केवल 13dB क्षीणन होता है। यदि आप उच्च डेटा दरों पर अधिक सिग्नल मार्जिन चाहते हैं, तो लंबी केबलों के लिए उच्च आवृत्तियों पर कम क्षीणन वाला केबल चुनें।

क्रॉसटॉक (उच्च आवृत्ति पैरामीटर मूल बातें 03- क्रॉसटॉक पैरामीटर)

एक सिग्नल या अंतर युग्म से दूसरे सिग्नल या अंतर युग्म में प्रेषित ऊर्जा की मात्रा। SAS केबलों के लिए, यदि निकट-अंत क्रॉसस्टॉक (NEXT) पर्याप्त छोटा नहीं है, तो यह अधिकांश लिंक समस्याओं का कारण बनेगा। NEXT का मापन केबल के केवल एक सिरे पर किया जाता है, और यह आउटपुट ट्रांसमिशन सिग्नल युग्म से इनपुट रिसीविंग युग्म में स्थानांतरित ऊर्जा की मात्रा है। दूर-अंत क्रॉसस्टॉक (FEXT) को केबल के एक सिरे पर ट्रांसमिशन युग्म के लिए एक सिग्नल इंजेक्ट करके और यह देखकर मापा जाता है कि केबल के दूसरे सिरे पर ट्रांसमिशन सिग्नल पर कितनी ऊर्जा शेष है।

केबल असेंबली और कनेक्टर में NEXT आमतौर पर सिग्नल डिफरेंशियल पेयर्स के खराब आइसोलेशन के कारण होता है, जो आउटलेट और प्लग, अधूरी ग्राउंडिंग, या केबल टर्मिनेशन एरिया के खराब संचालन के कारण हो सकता है। सिस्टम डिज़ाइनर को यह सुनिश्चित करना होगा कि केबल असेंबलर ने इन तीन समस्याओं का समाधान किया है।

24, 26 और 28 के सामान्य 100Ω केबलों के लिए हानि वक्र

"एसएफएफ-8410-एचएसएस कॉपर परीक्षण और प्रदर्शन आवश्यकताओं के लिए विनिर्देश" के अनुसार अच्छी गुणवत्ता वाली केबल असेंबली में NEXT 3% से कम होना चाहिए। जहाँ तक s-पैरामीटर का संबंध है, NEXT 28dB से अधिक होना चाहिए।

रिटर्न लॉस (उच्च आवृत्ति पैरामीटर मूल बातें 06- रिटर्न लॉस)

रिटर्न लॉस, सिग्नल के इंजेक्ट होने पर सिस्टम या केबल से परावर्तित ऊर्जा की मात्रा को मापता है। यह परावर्तित ऊर्जा केबल के प्राप्तकर्ता सिरे पर सिग्नल के आयाम में गिरावट का कारण बन सकती है और संचारित सिरे पर सिग्नल की अखंडता संबंधी समस्याएँ पैदा कर सकती है, जिससे सिस्टम और सिस्टम डिज़ाइनरों के लिए विद्युत चुम्बकीय हस्तक्षेप की समस्याएँ पैदा हो सकती हैं।

यह वापसी हानि केबल असेंबली में प्रतिबाधा बेमेल के कारण होती है। इस समस्या का सावधानीपूर्वक समाधान करके ही सिग्नल की प्रतिबाधा सॉकेट, प्लग और वायर टर्मिनल से गुजरते समय नहीं बदलेगी, जिससे प्रतिबाधा परिवर्तन न्यूनतम हो जाएगा। वर्तमान SAS-4 मानक को SAS-2 के ±10Ω प्रतिबाधा मान की तुलना में ±3Ω प्रतिबाधा मान पर अद्यतन किया गया है, और अच्छी गुणवत्ता वाले केबलों की आवश्यकताओं को 85 या 100±3Ω की नाममात्र सहनशीलता के भीतर रखा जाना चाहिए।

तिरछा विरूपण

SAS केबलों में, दो प्रकार की तिरछी विकृतियाँ होती हैं: अंतर युग्मों के बीच और अंतर युग्मों के भीतर (सिग्नल अखंडता सिद्धांत का अंतर संकेत)। सिद्धांत रूप में, यदि केबल के एक छोर पर कई सिग्नल प्रविष्ट होते हैं, तो उन्हें दूसरे छोर पर एक साथ पहुँचना चाहिए। यदि ये सिग्नल एक ही समय पर नहीं पहुँचते हैं, तो इस घटना को केबल का तिरछा विरूपण, या विलंब-तिरछा विरूपण कहा जाता है। अंतर युग्मों के लिए, अंतर युग्म के भीतर तिरछा विरूपण, अंतर युग्म के दो तारों के बीच का विलंब है, और अंतर युग्मों के बीच तिरछा विरूपण, अंतर युग्मों के दो सेटों के बीच का विलंब है। अंतर युग्म का बड़ा तिरछा विरूपण प्रेषित सिग्नल के अंतर संतुलन को बिगाड़ देगा, सिग्नल के आयाम को कम कर देगा, समय कंपन को बढ़ा देगा और विद्युत चुम्बकीय हस्तक्षेप की समस्याएँ पैदा करेगा। एक अच्छी गुणवत्ता वाले केबल का आंतरिक तिरछा विरूपण से अंतर 10ps से कम होना चाहिए।

पोस्ट करने का समय: 30 नवंबर 2023